# SUBJECT

Description and Use of the Muttics Processor.

SOFTWARE SUPPORTED!

All Multics Software Releases

DATE:

October, 1975

ORDER NUMBER:

AL39, Rev. 0

#### PREFACE

This document describes the Processor used in the Multics system. It is assumed that the reader is familiar with the overall modular organization of the Multics system and with the philosophy of asynchronous operation. In addition, this manual presents a thorough discussion of virtual memory addressing concepts including segmentation and paging.

The manual is intended for use by system programmers responsible for writing software to interface with the special virtual memory hardware and with the fault and interrupt portions of the hardware. It should also prove valuable to programmers who must use machine instructions (particularly language translator implementors) and to those persons responsible for analyzing crash conditions in System Dumps.

c 1974 Honeywell Information Systems, Inc.

REVIEW DRAFT Subject to Change October, 1975

# CONTENTS

|            |                                                                         | Page       |

|------------|-------------------------------------------------------------------------|------------|

|            |                                                                         | _          |

|            |                                                                         |            |

| Section I  | Introduction To Processor.                                              | 1-1<br>1-1 |

|            | Features of the Multics Processor • • • • • • • • • • • • • • • • • • • | 1-1        |

|            | Address Modification and Address Appending • • • •                      | 1-2        |

| _          | Faults and Interrupts                                                   | 1-2        |

|            | Summary of Processor Features                                           | 1-2        |

|            | Processor Hodes of Operation                                            | 1-3        |

|            | Instruction Hodes                                                       | 1-3        |

|            | Normal Mode                                                             | 1-3        |

|            | Privileged Mode                                                         | 1-4        |

|            | Addressing Modes                                                        | 1-4        |

|            | Absolute Mode                                                           | 1-4        |

|            | Append Mode                                                             | 1-4        |

|            | Bar Mode                                                                | 1-4        |

|            | Processor Unit Functions                                                | 1-5        |

|            | Appending Unit                                                          | 1-5        |

|            | Associative Memory Assemblies                                           | 1-5<br>1-6 |

|            | Control Unit                                                            | 1-6        |

|            | Decimal Unit                                                            | 1-6        |

|            | necimal nuit                                                            | 1-0        |

| <i>i</i>   |                                                                         |            |

| Section II | Machine Instructions                                                    | 2-1        |

|            | Instruction Repertoire                                                  | 2-1        |

|            | Basic Operations • • • • • • • • • • • • • • • • • • •                  | 2-1        |

|            | Extended Instruction Set (EIS) Operations                               | 2-1        |

|            | EIS Single-Word Operations                                              | 2-1        |

|            | EIS Multi-Word Operations                                               | 2-2<br>2-2 |

|            | Format of Instruction Description                                       | 2-4        |

|            | Main Store Addresses                                                    | 2-4        |

|            | Index Values                                                            | 2-4        |

|            | Abbreviations and Symbols                                               | 2-4        |

|            | Register Positions and Contents                                         | 2-5        |

|            | Other Symbols                                                           | 2-6        |

|            | Arrangement of Instructions                                             | 2-6        |

|            | Common Attributes of Instructions                                       | 2-6        |

|            | Illegal Modification                                                    | 2-6        |

|            | Parity Indicator                                                        | 2-6        |

|            | Instruction Word Formats                                                | 2-7        |

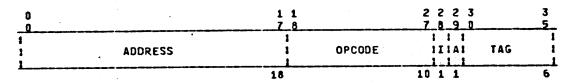

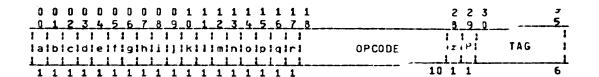

|            | Basic and EIS Single-Word Instructions                                  | 2-7        |

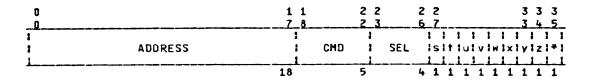

|            | Indirect Words                                                          | 2-8        |

|            |                                                                         |            |

|            |                                                                         |            |

|            |                                                                         |            |

|            |                                                                         |            |

|            | men M IAI Wand Pankauaki ana                                            | 2-0        |

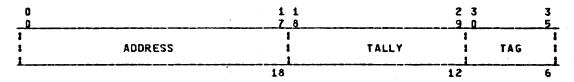

|            | EIS Multi-Word Instructions                                             | 2-9<br>2-9 |

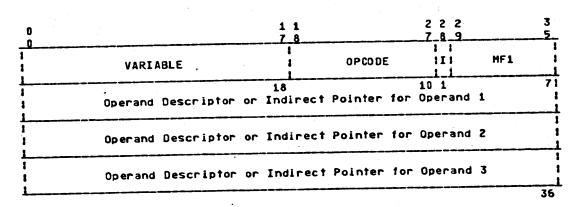

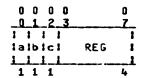

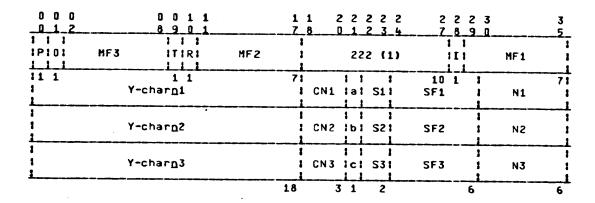

| •          | EIS Modification Fields (MF)                                            | 2-11       |

|            | Operand Descriptor Indirect Pointers • •                                | 2-11       |

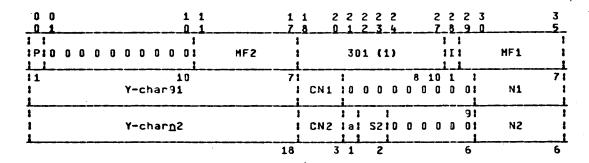

|            | Alphanumeric Operand Descriptor Format                                  | 2-12       |

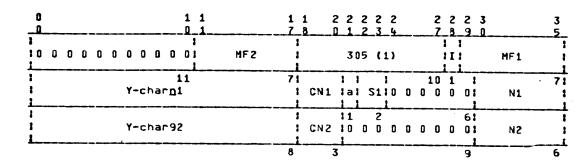

|            | Numeric Operand Descriptor Format • • • • • •                           | 2-14       |

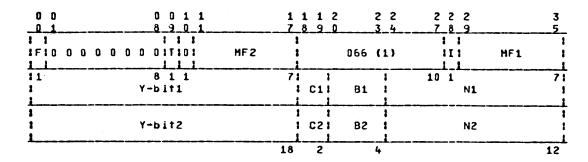

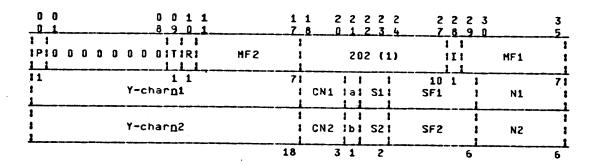

|            | Bit String Operand Descriptor Format                                    | 2-15       |

|            | Fixed Point Arithmetic Instructions                                     | 2-16       |

|            | Data Movement Load Instructions                                         | 2-16       |

|            | Data Movement Store Instructions                                        | 2-25       |

|            |                                                                         |            |

|                                                                                       | Page           |

|---------------------------------------------------------------------------------------|----------------|

| Data Movement Shift Instructions                                                      | 2-34           |

| Addition Instructions                                                                 | 2-40           |

| Subtraction Instructions                                                              | 2-48           |

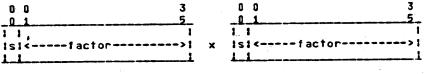

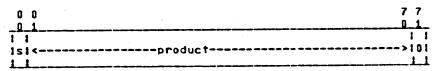

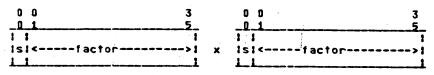

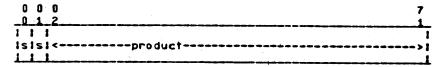

| Multiplication Instructions                                                           | 2-55           |

| Division Instructions                                                                 | 2-57<br>2-60   |

| Comparison Instructions                                                               | 2-61           |

| Miscellaneous Instructions                                                            | 2-66           |

| Boolean Operation Instructions                                                        | 2-67           |

| AND Instructions                                                                      | 2-67           |

| OR instructions.                                                                      | 2-70           |

| Exclusive OR Instructions                                                             | 2-73<br>2-76   |

| Comparative NOT Instructions                                                          | 2-78           |

| Floating Point Arithmetic Instructions                                                | 2-80           |

| Data Hovement Load Instructions                                                       | 2-80           |

| Data Movement Store Instructions                                                      | 2-81           |

| Addition Instructions                                                                 | 2-84           |

| Subtraction Instructions                                                              | 2-87<br>2-90   |

| Multiplication Instructions                                                           | 2-93           |

| Negate Instructions.                                                                  | 2-97           |

| Normalize Instructions                                                                | 2-98           |

| Round Instructions                                                                    | 2-99           |

| Compare Instructions                                                                  | 2-101          |

| Miscellaneous Instructions                                                            | 2-103          |

| Transfer Instructions                                                                 | 2-105          |

| Pointer Register Instructions                                                         | 2-117<br>2-117 |

| Data Movement Store Instructions                                                      | 2-121          |

| Address Arithmetic Instructions                                                       | 2-124          |

| Miscellaneous Instructions                                                            | 2-125          |

| Miscellaneous Instructions                                                            | 2-126          |

| Calendar Clock Instruction.                                                           | 2-126          |

| Derail Instruction                                                                    | 2-127<br>2-128 |

| Execute Instructions                                                                  | 2-130          |

| No Operation Instructions                                                             | 2-133          |

| Repeat Instructions                                                                   | 2-135          |

| Ring Alarm Register Instruction                                                       | 2-144          |

| Store Base Address Register Instruction                                               | 2-145          |

| Translation Instructions                                                              | 2-146<br>2-148 |

| Privileged Instructions                                                               | 2-148          |

| Register Store Instructions                                                           | 2-155          |

| Clear Associative Memory Instructions                                                 | 2-162          |

| Configuration and Status Instructions                                                 | 2-164          |

| System Control Instructions                                                           | 2-167          |

| Miscellaneous Instructions                                                            | 2-171          |

| •                                                                                     |                |

| Extended Instruction Set (EIS)                                                        | 2-172          |

| Address Register Load Instructions                                                    | 2-172          |

| Address Register Store Instructions                                                   | 2-175          |

| Address Register Special Arithmetic Instructions .  Alphanumeric Compare Instructions | 2-178<br>2-186 |

| Alphanumeric Hove Instructions                                                        | 2-100          |

| Numeric Compare Instruction                                                           | 2-205          |

| Numeric Move Instructions                                                             | 2-208          |

| Bit String Combine Instructions                                                       | 2-213          |

| Bit String Compare Instructions                                                       | 2-217          |

| ,             |                                                          | Page             |

|---------------|----------------------------------------------------------|------------------|

|               |                                                          |                  |

|               |                                                          | 0.040            |

|               | Bit String Set Indicators Instructions • • • • •         | 2-219<br>2-221   |

|               | Data Conversion Instructions                             | 2-225            |

|               | Decimal Addition Instructions                            | 2-231            |

| •             | Decimal Multiplication Instructions                      | 2-234            |

|               | Decimal Division Instructions • • • • • • •              | 2-237            |

|               | Micro Operations for Edit Instructions                   | 2-240            |

|               | Micro Operation Sequence                                 | 2-240            |

|               | Edit Insertion Table                                     | 2-241            |

|               | Edit Flags                                               | 2-241            |

| ·             | Terminating Nicro Operations                             | 2-242            |

|               | MVNE and MVE Differences                                 | 2-242            |

| ` .           | Numeric Edit                                             | 2-242            |

|               | Alphanumeric Edit                                        | 2-242<br>2-243   |

|               | Micro Operators                                          | 2-243            |

|               | Micro Operation Code Assignment Map                      | 2-290            |

|               |                                                          |                  |

| Section III   | Data Representation                                      | 3-1              |

| Jec 11011 111 | Information Organization                                 | 3-1              |

|               | Position Numbering                                       | 3-1              |

|               | Number System                                            | 3-1              |

|               | Information Formats                                      | 3-2              |

|               | Data Parity                                              | 3-4              |

|               | Representation of Data                                   | 3-5              |

|               | Numeric Data                                             | 3-5              |

| •             | Fixed Point Binary Data                                  | 3-5<br>3-5       |

|               | Fixed Point Binary Integers                              | 3-5<br>3-6       |

|               | Fixed Point Binary Fractions                             | 3-8              |

|               | Floating Point Binary Data                               | 3-9              |

|               | Normalized Numbers                                       | 3-9              |

|               | Decimal Data                                             |                  |

|               | Decimal Data Values                                      |                  |

|               | Decimal Zero                                             | 3-14             |

|               | Alphanumeric Data                                        | 3-14             |

|               | Character String Data                                    | 3-14             |

|               | Bit String Data                                          | 3-15             |

|               |                                                          |                  |

|               |                                                          | 4-1              |

| Section IV    | Program Accessible Registers                             |                  |

|               | Accumulator Register (A)                                 |                  |

|               | Quotient Register (Q)                                    |                  |

|               | Exponent Register (E)                                    | 4-4              |

|               | Exponent Accumulator-Quotient Register (EAQ)             | 4-4              |

|               | Index Registers (Xn)                                     | 4-5              |

|               | Indicator Register (IR)                                  | 4-5              |

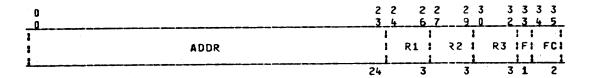

|               | Base Address Register (BAR)                              | 4-9              |

|               |                                                          |                  |

|               |                                                          |                  |

|               |                                                          |                  |

|               |                                                          |                  |

|               |                                                          | ÷ .              |

|               | Timer Register (TR)                                      | . 4-9            |

|               | Ring Alarm Register (RALR)                               | . 4-10           |

|               | Pointer Registers (PRN)                                  | . 4-11           |

|               | Procedure Pointer Register (PPR)                         | . 4-13           |

|               | Temporary Pointer Register (TPR)                         | . 4-15           |

|               | Descriptor Segment Base Register (DSBR, DBR)             | • 4-16<br>• 4-18 |

|               | Segment Descriptor Word Associative Memory (SDWAM).      | • 4-10<br>• 4-21 |

|               | Page Table Word Associative Memory (PTWAM)               | 4-23             |

|               | Fault Register                                           |                  |

|               | mode Kedtziel flukto o o o o o o o o o o o o o o o o o o |                  |

|             |                                                     | Page         |

|-------------|-----------------------------------------------------|--------------|

|             | •                                                   |              |

|             | Cache Hode Register (CHR)                           | 4-28         |

|             | Control Unit (CU) History Registers                 | 4-29         |

|             | Operations Unit (OU) History Registers              | 4-32         |

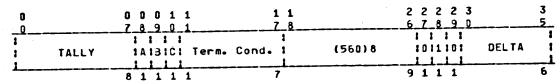

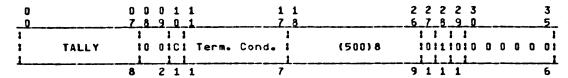

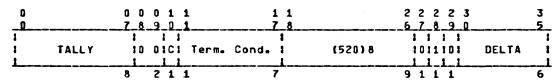

|             | Decimal Unit (DU) History Registers                 | 4-34         |

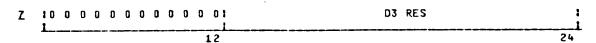

|             | Appending Unit (AU) History Registers               | 4-37         |

|             | Configuration Switch Data                           | 4-39         |

|             | Decimal Unit Data                                   | 4-40         |

|             |                                                     | 4-45         |

| Section V   | Addressing as Saggerhankton as to a                 |              |

| 30011011    | Addressing Segmentation and Paging                  | 5-1          |

| •           | Absolute Mode.                                      | 5-1          |

|             | Append Mode.                                        | 5-1<br>5-2   |

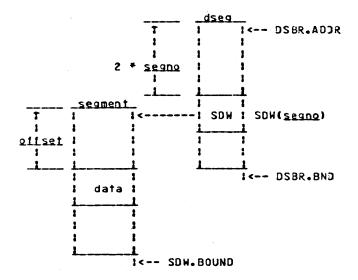

|             | Segmentation                                        | 5-2          |

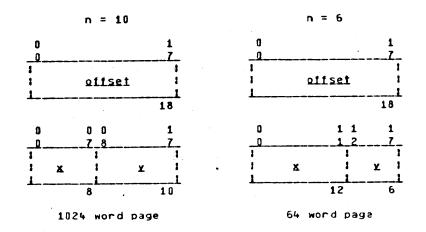

|             | Paging                                              | 5-3          |

|             | Changing Addressing Modes                           | 5-6          |

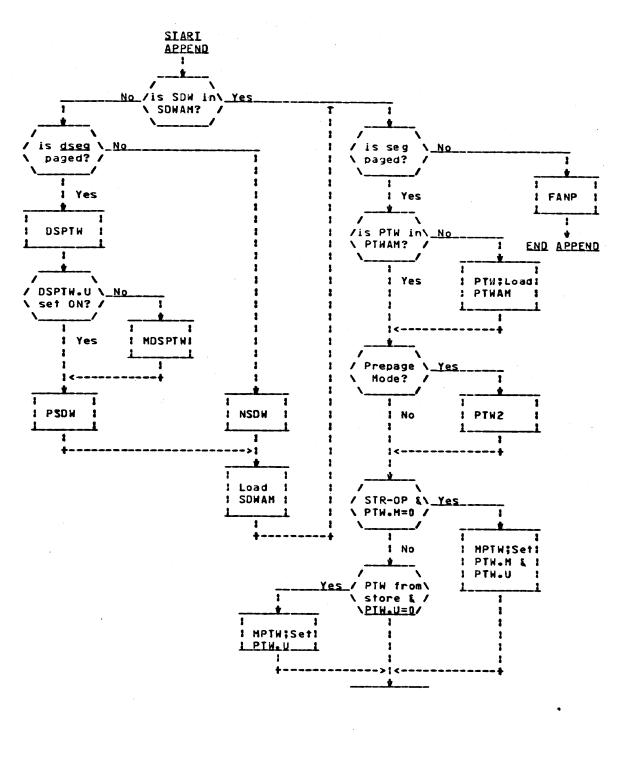

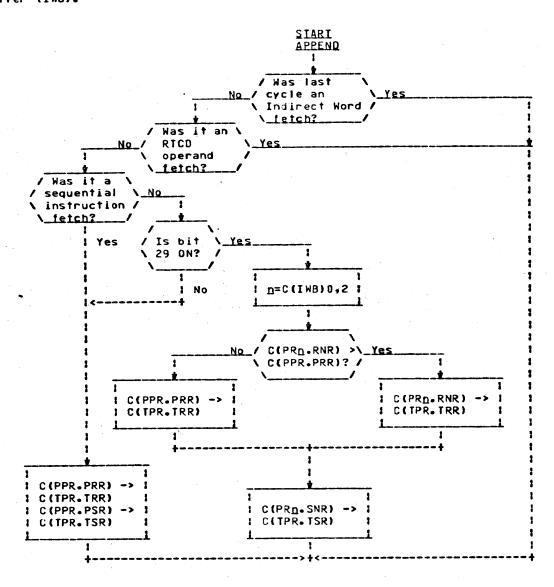

|             | Address Appending                                   | 5-7          |

| Y           | Address Appending Sequences.                        | 5-7          |

| •           | Appending Unit Data Word Formats                    | 5-10         |

|             | Segment Descriptor Word (SDW) Format                | 5-10         |

|             | Page Table Word (PTW) Format                        | 5-11         |

|             |                                                     |              |

| Section VI  | Effective Address Formation                         | 6-1          |

|             | Definition of Effective Address                     | 6-1          |

| •           | Types of Effective Address Formation                | 6-1          |

|             | Effective Address Formation Description             | 6-2          |

|             | Effective Address Formation Involving Offset Only . | 6-2          |

|             | The Address Modifier (TAG) Field                    | 6-2          |

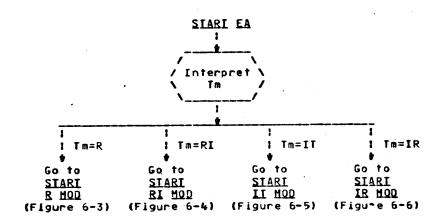

|             | Effective Address Formation Flowcharts              | 6-2          |

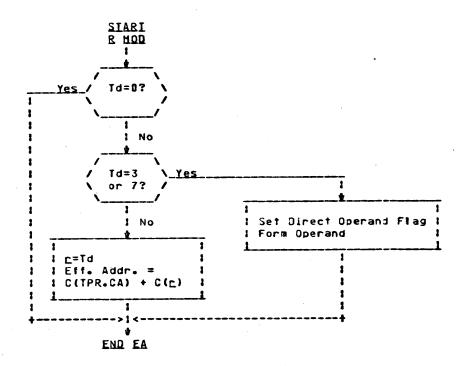

|             | Register (R) Modification.                          | 6-4          |

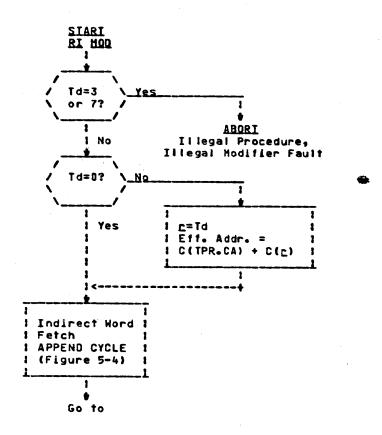

|             | Register Then Indirect (RI) Modification            | 6-4          |

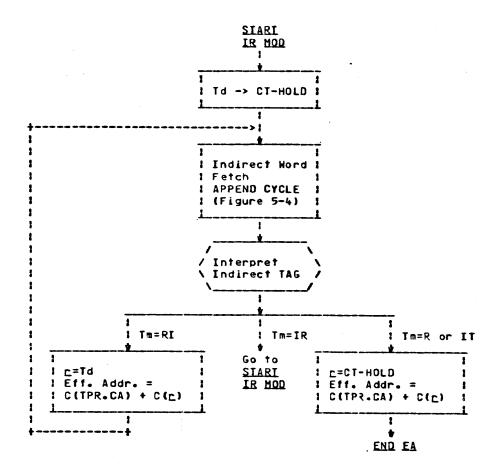

|             | Indirect Then Register (IR) Modification            | 6-6<br>6-8   |

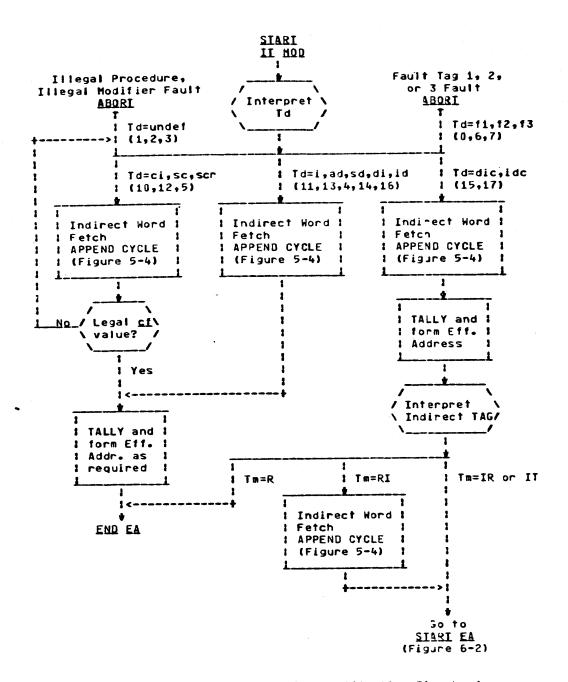

|             | Indirect Then Tally (IT) Modification               | 6-9          |

|             | Effective Address Formation Involving Both          | <b>5</b>     |

|             | Segment Number and Offset                           | 6-15         |

|             | The Use of Bit 29 of the Instruction Words          | 6-16         |

|             | Special Modifiers                                   | 6-16         |

|             | Indirect to Pointer (itp) Modification              | 6-17         |

|             | Indirect to Segment (its) Modification              | 6-18         |

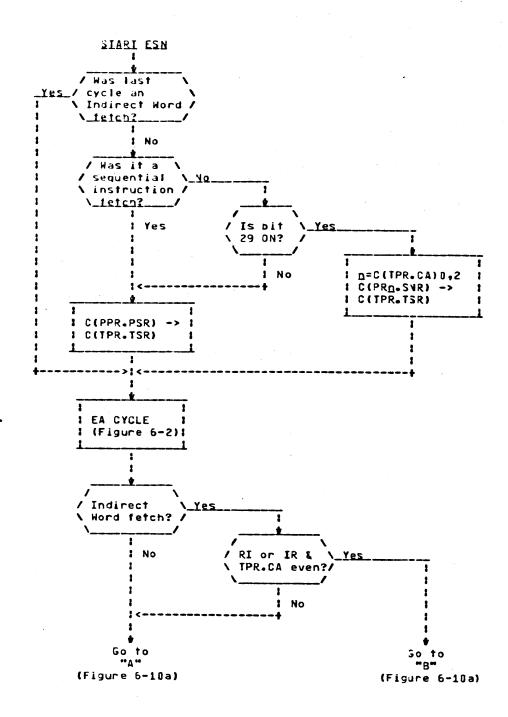

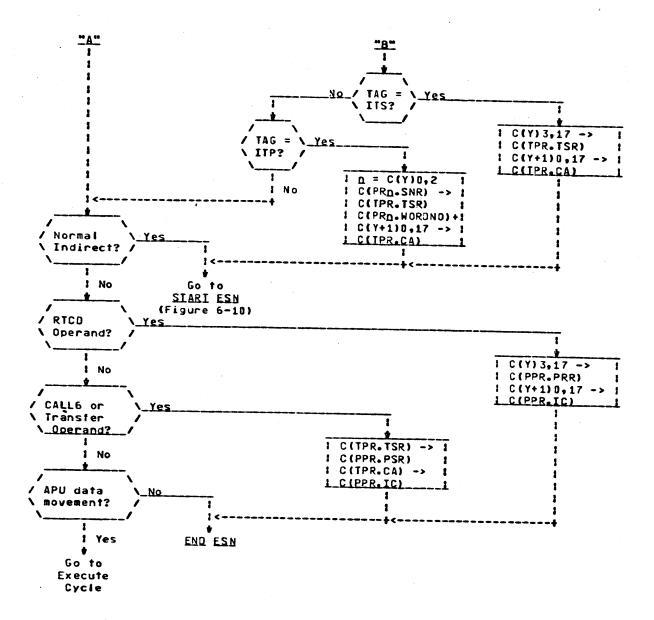

|             | Effective Segment Number Generation.                | 6-19         |

|             | Effective Address Formation for Extended            |              |

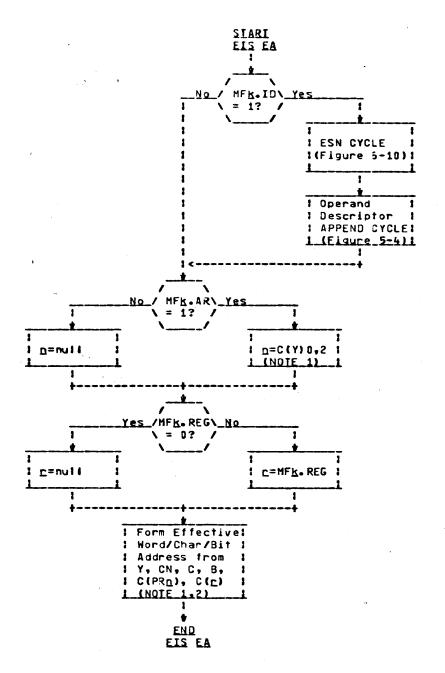

|             | Instruction Set                                     | 6-21         |

|             | Character- and Bit-String Address Arithmetic        | 6-23         |

|             | Algorithms                                          | 6-27         |

|             | 9-Bit Character String Address Arithmetic           | 6-23<br>6-24 |

|             |                                                     | 0-24         |

|             |                                                     |              |

|             |                                                     |              |

|             |                                                     |              |

|             | 6-Bit Character String Address Arithmetic           | 6-24         |

|             | 4-Bit Character String Address Arithmetic           | 6-24         |

|             | Bit String Address Arithmetic                       | 6-24         |

|             |                                                     |              |

| Section VII | Faults and Interrupts                               | 7-1          |

|             | Fault Cycle Sequence                                | 7-1          |

|             | Fault Priority.                                     | 7-2          |

|             | Fault Recognition                                   | 7-3          |

|             | I GUIT UESCLIDIIONS A A A A A A A A                 | 7 - 1.       |

REVIEW DRAFT Subject to Change October, 1975

|              |                                                 | Pa  |

|--------------|-------------------------------------------------|-----|

|              | Group 1 Faults                                  | 7-  |

|              | Group 2 Faults                                  | 7-  |

|              | Group 3 Faults                                  | 7-  |

|              | Group 4 Faults                                  | 7-  |

|              | Group 5 Faults                                  | 7-  |

|              | Group 6 Faults                                  | 7-  |

|              | Group 7 Faults                                  | 7-  |

|              | Program Interrupts and External Faults          | 7-  |

|              | Execute Interrupt Sampling                      | 7-  |

|              | Execute Interrupt Cycle Sequence                | 7-  |

| Section VIII | Hardware Ring Implementation                    | 8 - |

|              | Ring Protection Philosophy                      | 8-  |

|              | Ring Protection in Multics                      | 8   |

|              | Ring Protection in the Multics Processor        | 8-  |

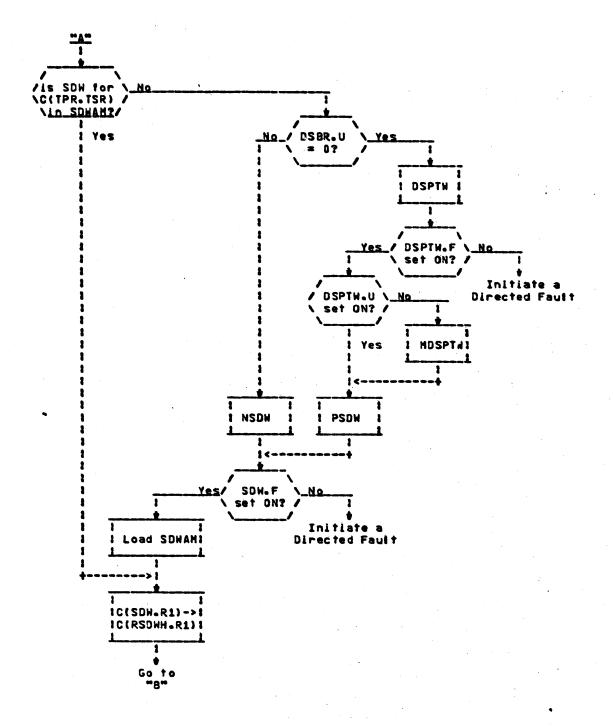

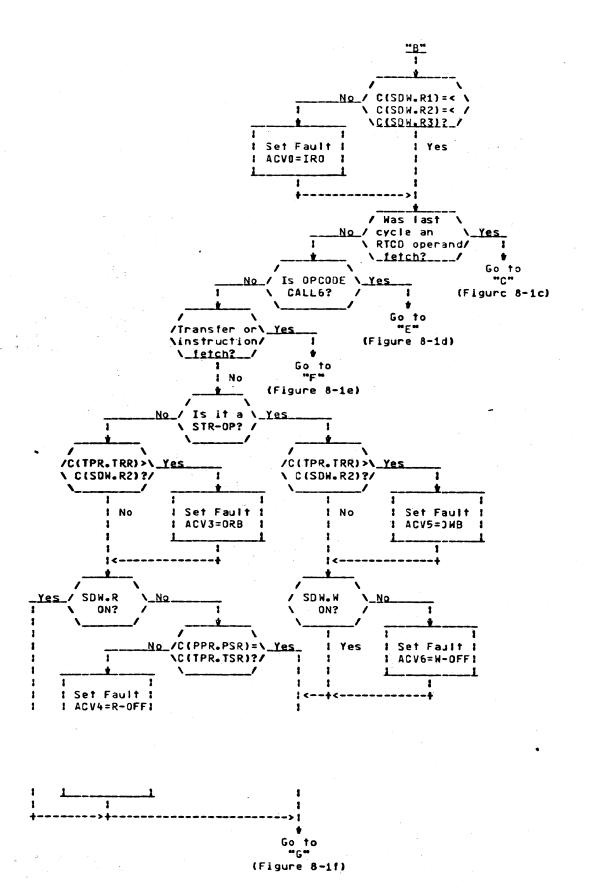

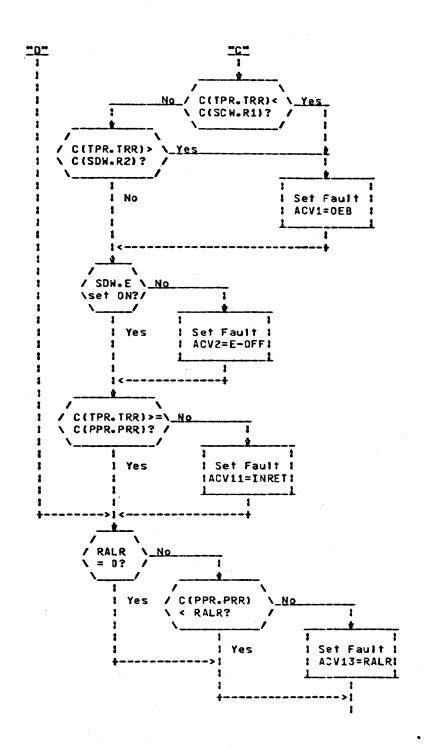

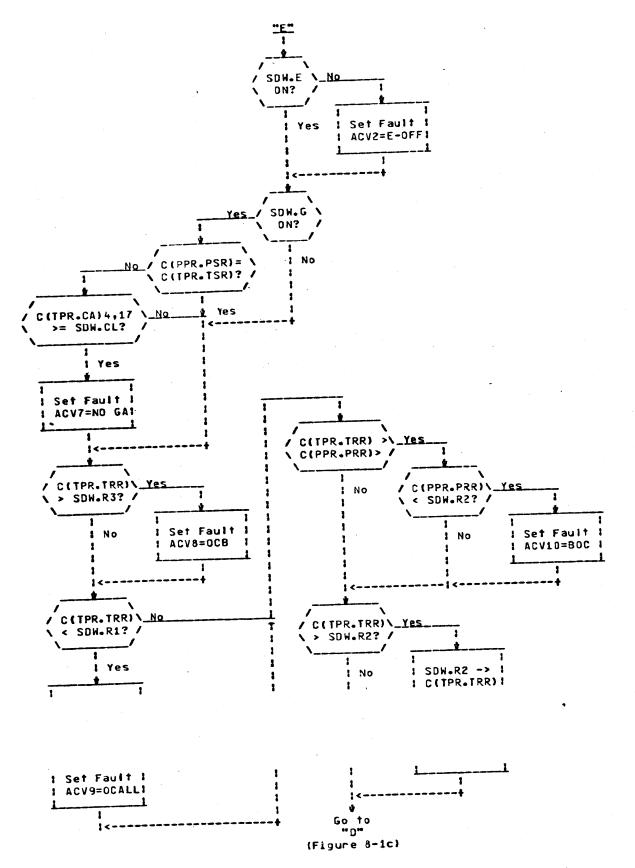

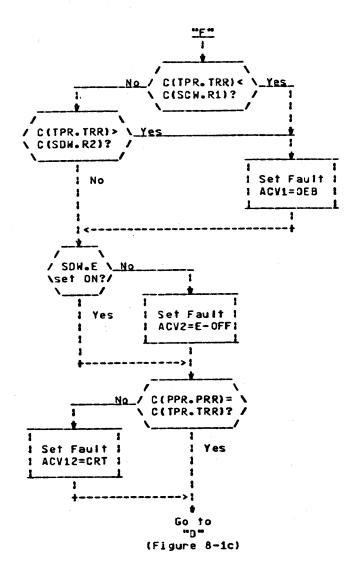

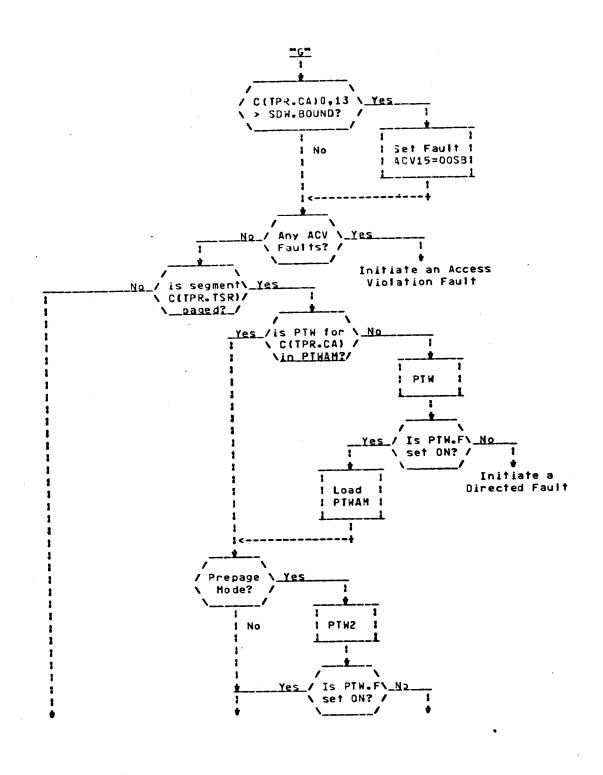

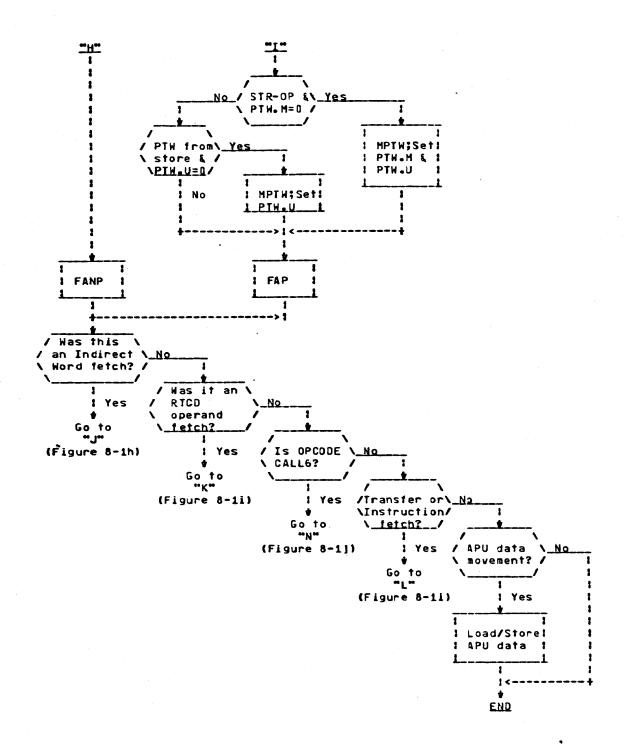

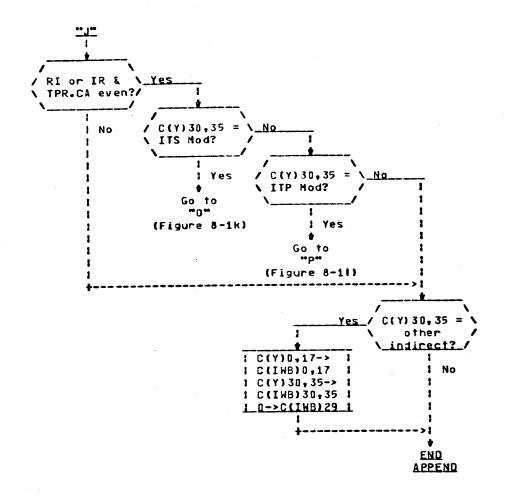

|              | Appending Unit Operation with Ring Mechanism    | 8   |

| Section IX   | Cache Store Operation                           | 9.  |

|              | Philosophy of Cache Store                       | g.  |

|              | Cache Store Organization                        | 9.  |

|              | Cache Store/Main Store Mapping                  | g.  |

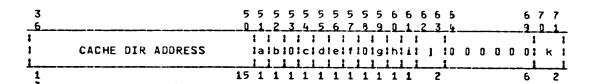

|              | Cache Store Addressing                          | 9   |

|              | Cache Store Control                             | g.  |

|              | Enabling and Disabling Cache Store              | ģ.  |

|              | Cache Store Control in Segment Descriptor Words | ģ.  |

|              | Loading the Cache Store                         | ģ   |

|              | General Clear                                   | g.  |

|              | Selective Clear                                 | 9   |

|              | Dumping the Cache Stone.                        | Q.  |

|                  |             |                                                                             | Page         |

|------------------|-------------|-----------------------------------------------------------------------------|--------------|

| Append.          | i× A        | Operation Code Map                                                          | A-1          |

| Append           |             | Alphabetic Operation Code List                                              |              |

|                  |             | Add M 1161                                                                  | B-1          |

| Append.          | ıx c        | Address Modifiers                                                           | C-1          |

|                  |             |                                                                             | •            |

|                  | a.          | ILLUSTRATIONS                                                               |              |

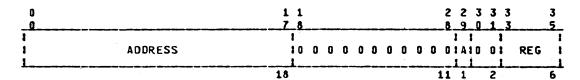

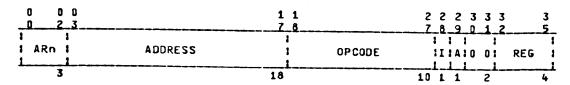

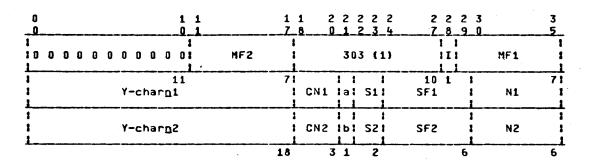

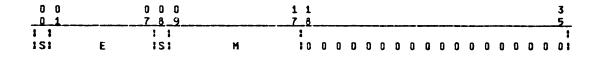

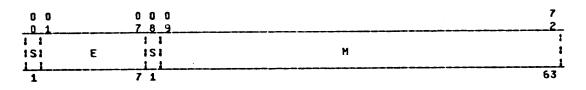

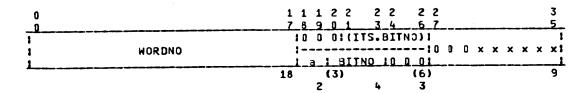

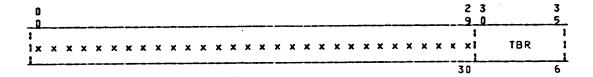

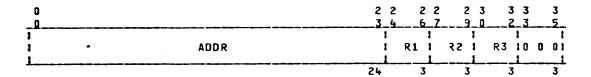

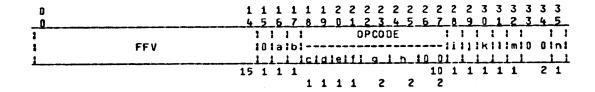

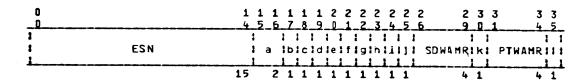

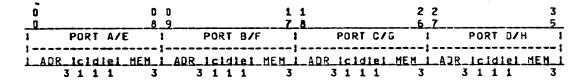

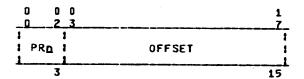

| Figure           | 2-1 .       | Basic and EIS Single-Word Instruction Format                                | 2-7          |

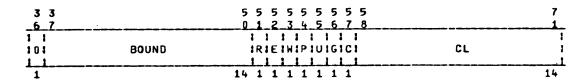

| Figure           |             | Indirect Word Format                                                        | 2-8          |

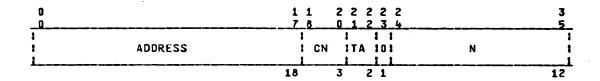

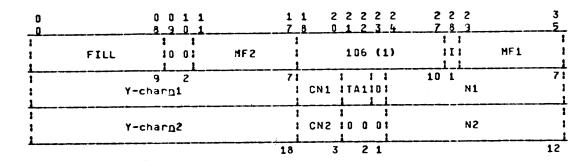

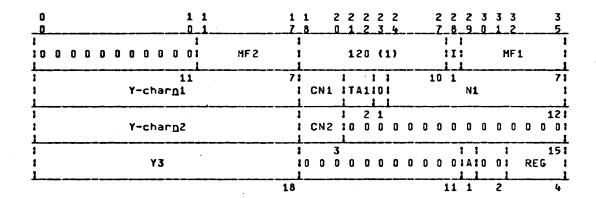

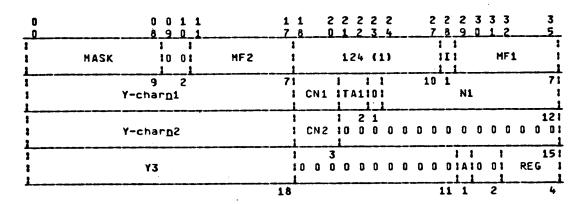

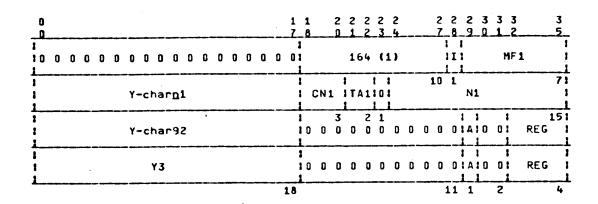

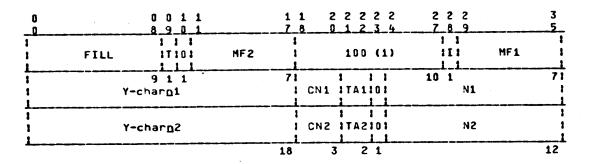

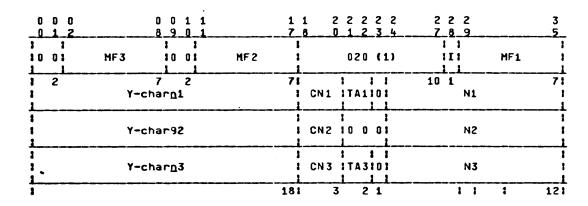

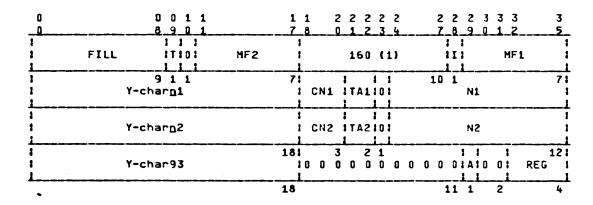

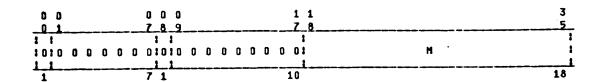

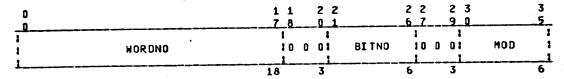

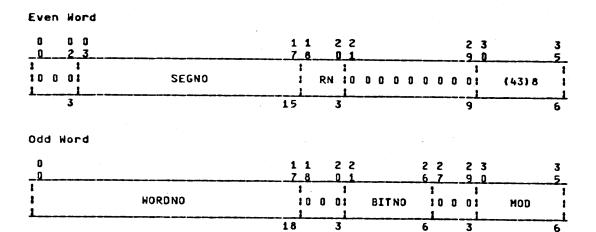

| Figure           |             | EIS Multi-Word Instruction Format.                                          | 2-9          |

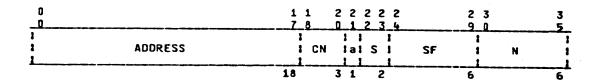

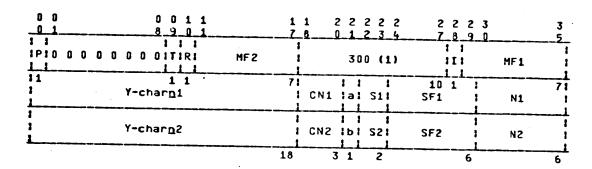

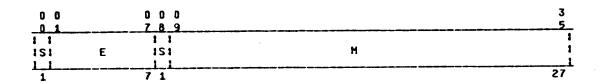

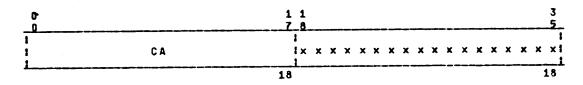

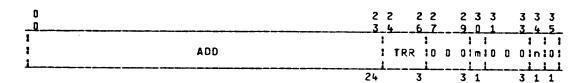

| Figure<br>Figure | _           | EIS Modification Field (MF) Format                                          | 2-10         |

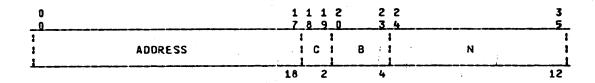

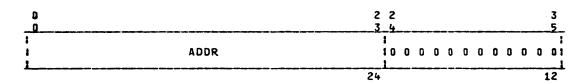

| Figure           |             | Operand Descriptor Indirect Pointer Format                                  | 2-12         |

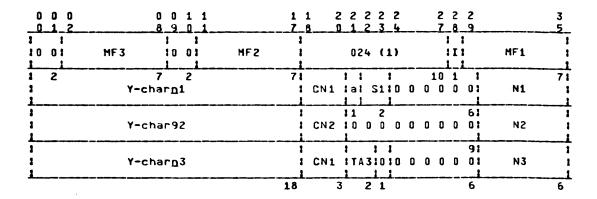

| Figure           | -           | Numaric Openand Decementary Course                                          | 2-12<br>2-14 |

| Figure           |             | Bit String Operand Descriptor Format                                        | 2-15         |

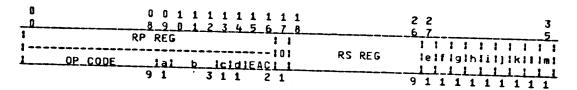

| Figure           | 2-9         | Repeat Double (RPD) Instruction Word Format                                 | 2-135        |

| Figure           |             | Repeat Link (RPL) Instruction Word Format                                   | 2-138        |

| Figure           |             | Repeat (RPT) Instruction Word Format                                        | 2-141        |

| Figure           |             | EIS Address Register Special Arithmetic Instruction Format.                 | 2-178        |

| Figure           | 2-13        | Compare Alphanumeric Strings (CMPC) EIS Multi-Word Instruction Format       | 2-186        |

| Figure           | 2-14        | Scan Characters Double (SCD) EIS Multi-Word Instruction Format              | 2-188        |

| Figure           | 2-15        | Scan with Mask (SCM) EIS Multi-Hord Instruction Format .                    | 2-191        |

| Figure           | 2-16        | Test Character and Translate (TCT) EIS Multi-Word Instruction Format        | 2-194        |

| Figure           | 2-17        | Nove Alphanumeric Left to Right (MLR) EIS Multi-Word Instruction Format.    | 2-197        |

| Figure           | 2-18        | Move Alphanumeric Edited (MVE) EIS Multi-Word Instruction Format.           | 2-200        |

| Figure           | 2-19        | Hove Alphanumeric with Translation (MVT) EIS Multi-Word Instruction Format. | 2-202        |

| Figure           | 2-20        | Compare Numeric (CMPN) EIS Multi-Word Instruction Format                    | 2-205        |

| Figure           | 2-21        | Hove Numeric (MVN) EIS Multi-Word Instruction Format                        | 2-208        |

| Figure           | 2-22        | Move Numeric Edited (MVNE) EIS Multi-Word Instruction Format                | 2-211        |

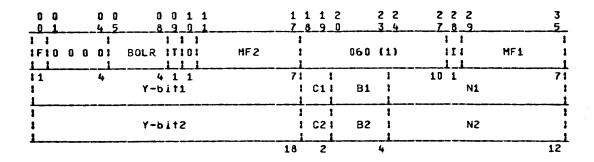

| Figure           | 2-23        | Combine Bit Strings Left (CSL) EIS Multi-Word Instruction Format            | 2-213        |

| Figure           | 2-24        | Compare Bit Strings (CMPB) EIS Multi-Word Instruction Format.               | 2-217        |

| Figure           | 2-25        | Binary to Decimal Convert (BTD) EIS Multi-Word Instruction Format.          | 2-221        |

| Figure           | 2-26        | Decimal to Binary Convert (DTB) EIS Multi-Hord                              | C-551        |

|                  |             |                                                                             |              |

|                  |             |                                                                             |              |

|                  |             | Instruction Format                                                          | 2-223        |

| Figure           | 2-27        | Add Using 2 Decimal Operands (AD2D) EIS Multi-Word Instruction Format.      | 2-225        |

| Figure           | 2-28        | Add Using 3 Decimal Operands (AD3D) EIS Multi-Word Instruction Format.      | 2-228        |

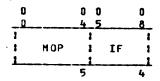

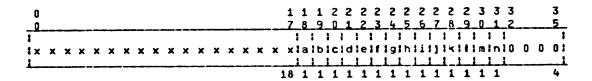

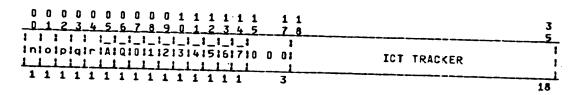

| Figure           |             | Micro Operation (MOP) Character Format                                      | 2-240        |

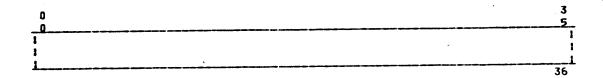

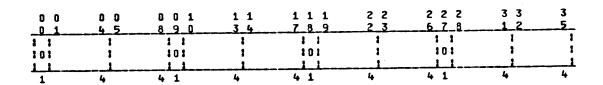

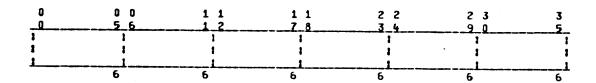

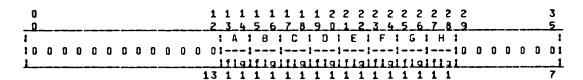

| Figure           |             | Unstructured Machine Word Format                                            | 3-2          |

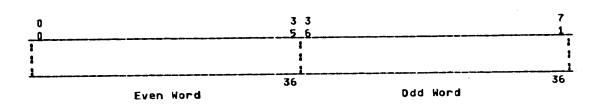

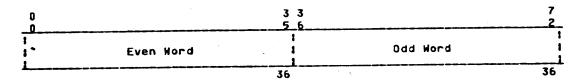

| Figure           |             | Unstructured Word Pair Format                                               | 3-3          |

| Figure           |             | Unstructured 4-bit Character Format                                         | 3-3          |

| Figure           | J <b>-4</b> | Unstructured 6-bit Character Format                                         | 3-3          |

REVIEW DRAFT Subject to Change October: 1975

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        | Page |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|

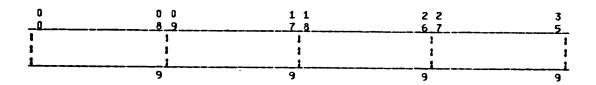

| Figure           | 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Unstructured 9-bit Character Format                                                    |      |

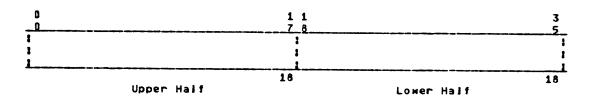

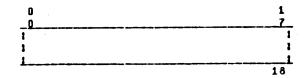

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Unstructured 18-bit Half Word Format                                                   | 3-4  |

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Upper 18-bit Half Word Floating Point Binary Operand                                   | 3-4  |

| Figure           | 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Format                                                                                 | 3-8  |

| 3                | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Format.                                                                                |      |

| Figure           | 3-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Formate                                                                                | 3-8  |

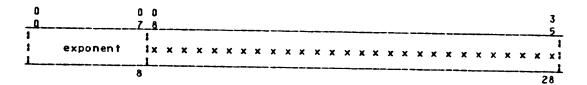

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Single Precision Floating Point Binary Operand Format.                                 | 3-9  |

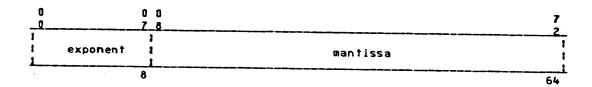

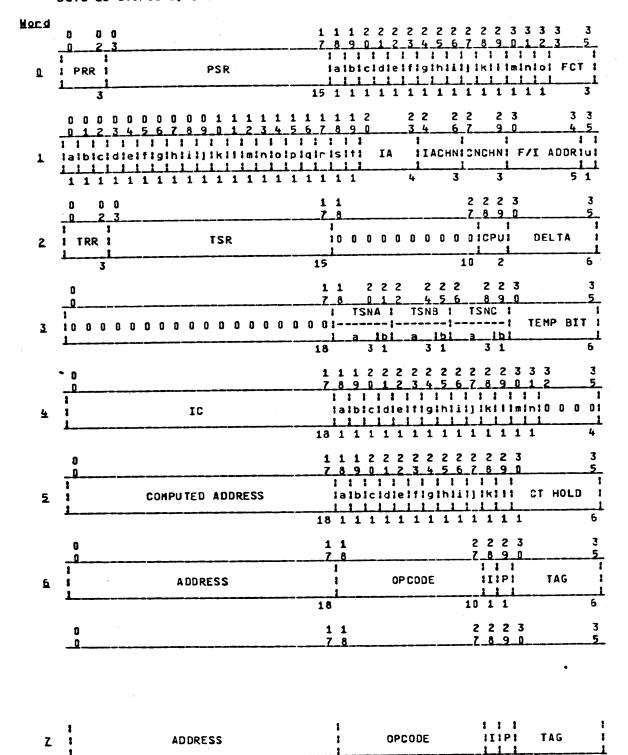

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Double Precision Floating Point Binary Operand Format. Accumulator Register (A) Format | 3-9  |

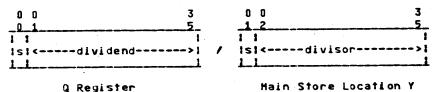

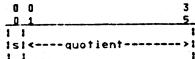

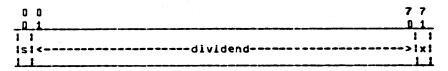

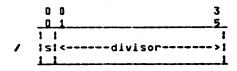

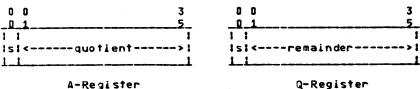

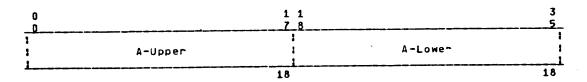

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Quotient Register (Q) Format                                                           | 4-2  |

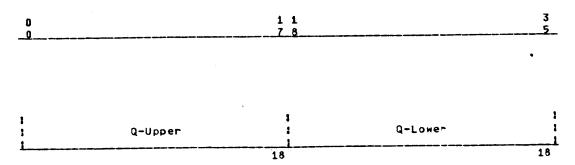

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Accumulator-Quotient Register (AQ) Format.                                             | 4-2  |

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Exponent Register (E) Format                                                           | 4-3  |

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Exponent-Accumulator-Quotient Register (EAQ) Format.                                   | 4-4  |

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Index Pagiston (Va) Farmat                                                             | 4-4  |

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Indicator Perictor (TD) Comma                                                          | 4-5  |

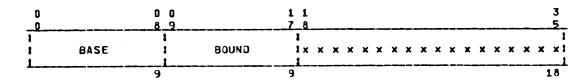

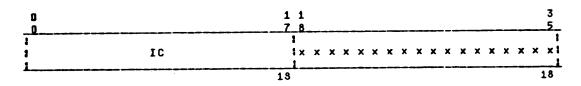

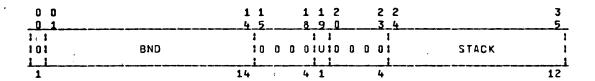

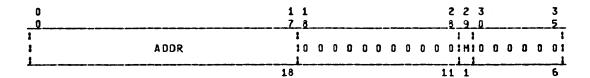

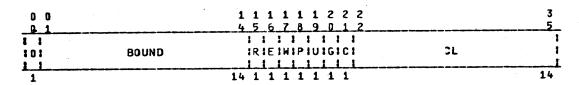

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Base Address Register (BAR) Format                                                     | 4-5  |

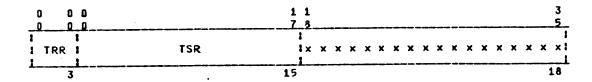

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Timer Register (TR) Format                                                             | 4-9  |

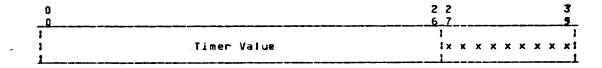

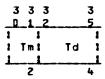

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ring Alarm Register (RALR) Format                                                      | 4-9  |

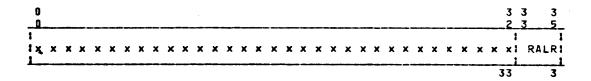

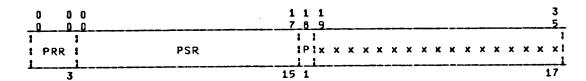

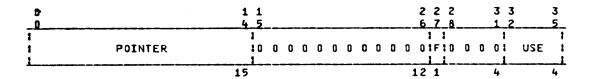

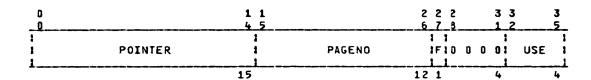

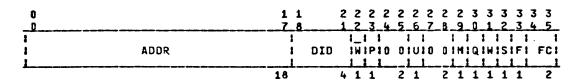

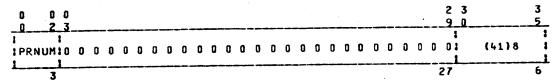

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pointer Register (PRn) Format.                                                         | 4-10 |

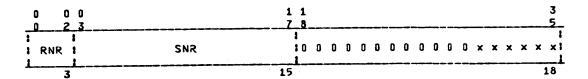

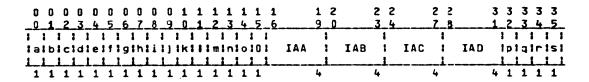

| Figure           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Procedure Pointer Register (PPR) Format.                                               | 4-11 |